# Korea's Contributions to the CMS Endcap Timing Layer for the HL-LHC Upgrade

CHANG-SEONG MOON

Representative of Korea CMS team

Centre for High Energy Physics (CHEP), Kyungpook National University (KNU)

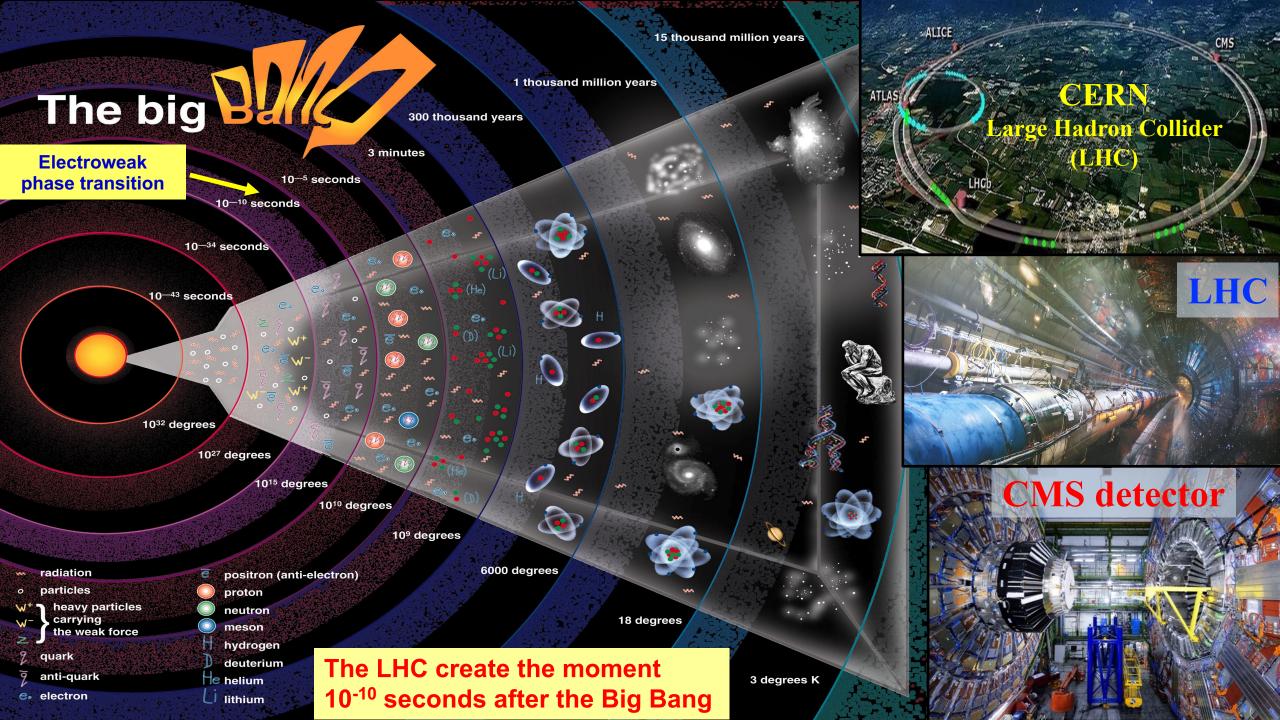

# High-Luminosity LHC (HL-LHC) at CERN

### **Goal**: precision tests of the standard model and Higgs physics, and searches for (rare) BSM phenomena

- Precision measurement of Higgs boson couplings (few percent)

- □ Measurement of the **Higgs boson self-coupling** via direct observation of the di-Higgs boson production

- □ Search for heavy dark matter candidates, SUSY particles, new gauge bosons, Long-Lived Particles, ...

#### Means: upgrade of the LHC optics and injectors to increase the beam intensity

- □ Luminosity delivered by LHC (2009-2026): ~ 400 fb<sup>-1</sup> / experiment [~250 fb<sup>-1</sup> collected so far]

- □ Target luminosity for HL-LHC (2030-2042): >3000 fb<sup>-1</sup> / experiment [one year of HL-LHC equivalent to ~10 years of LHC]

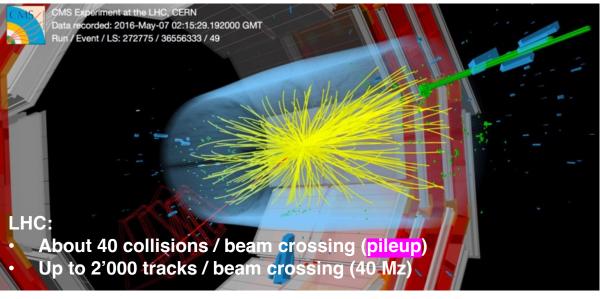

#### Collision event with 35 reconstructed vertices

#### Real life event at the LHC emulating HL-LHC conditions

# MIP Timing Detector (MTD) for CMS Phase-2 Upgrade

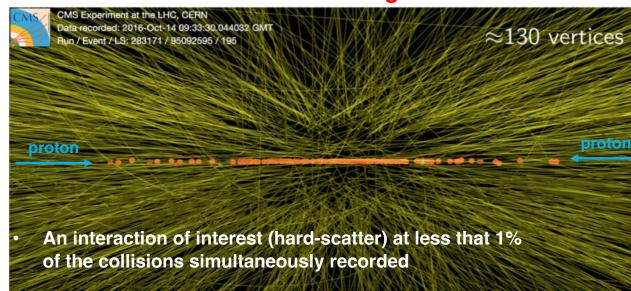

- □ Important to maintain detector performance during HL-LHC running

- Time information will help to reduce pileup effects from approximately 200 simultaneous interactions

- MIP timing detector (MTD) consists of barrel timing layer (BTL) and endcap timing layer (ETL), providing 30-50 ps time resolution per track

- BTL: LYSO crystal scintillator + SiPM readout

- ETL: Silicon based sensor (LGAD) + ASIC readout

- Two different detector technologies for radiation hardness and costs

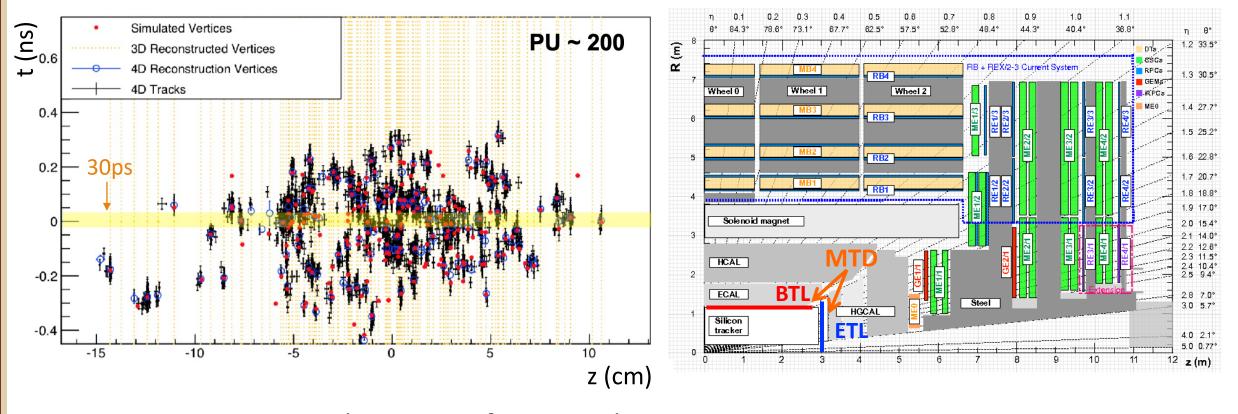

# Mip Timing Detector (MTD)

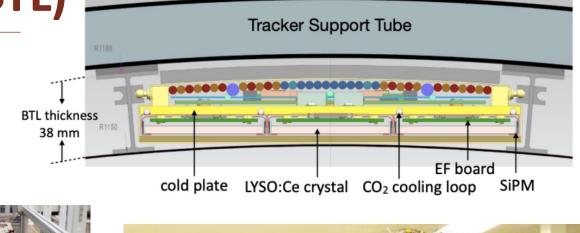

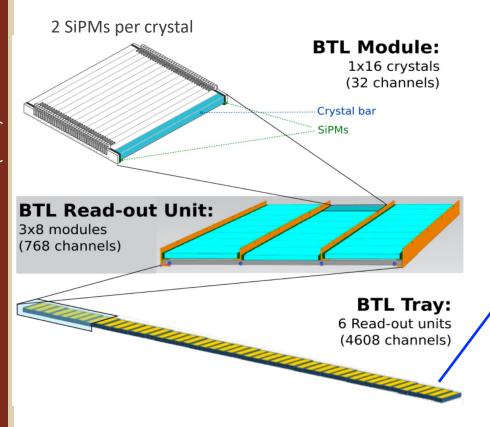

# MTD Barrel Timing Layer (BTL)

- □ 3.8 cm thin cylindrical detector

- $\circ$  located inside the tracker support tube,  $|\eta| < 1.45$

- ∘ ~5 m long, 38 m<sup>2</sup> surface

■ BTL construction: starting in early 2024!

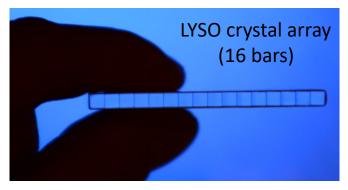

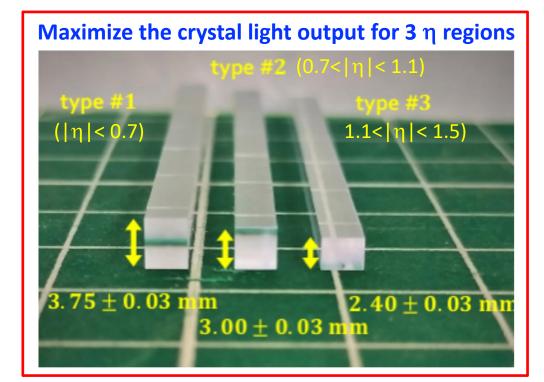

# BTL sensors: LYSO crystal

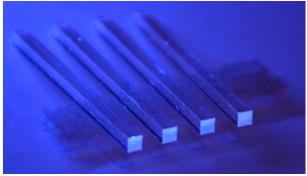

- □ LYSO crystal bars (166k)

- Cerium-doped lutetium yttrium orthosilicate (LYSO:Ce) scintillation medium

- Well established in PET applications and vendors widely available

- High radiation tolerance

- $\circ$   $\tau_{rise}$  : ~100 ps,  $\tau_{decay}$  : ~ 40 ns

- High Light Yield: 40000 γ/MeV

#### LYSO current status

- Single vendor selected

- Considerably better offer

- One of best vendor for performance-wise

- Reliable vendor (large production capacity)

- Pre-production in progress

- Ordered in March (2% of the total LYSO arrays)

- QA/QC and construction database ready

## **BTL** sensors : SiPM

- $\square$  SiPM (166k x 2 = 332k channel)

- Well consolidated technology

- Photon Detection Efficiency (PDE): 20–40%

- Compact, robust, insensitive to magnetic fields

- Good radiation hardness

- Fast recovery time <10 ns</li>

- High dynamic range (10<sup>5</sup>)

- □ SiPM current status

- Optimized cell size (25 μm) as a default for BTL

- Additional performance gain to boost signal

- SiPM die size (3.8×2.9 mm²) fixed to match with the thickest LYSO geometry

- □ SiPM plans

- Tender starts in July

- Sign the production contract in September

- First batch delivered ~ Feb. 2024 (for 7 months)

### SiPM Module

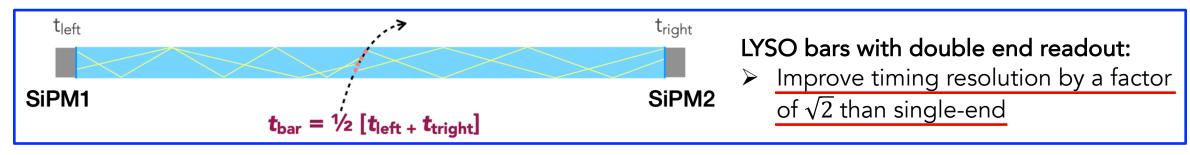

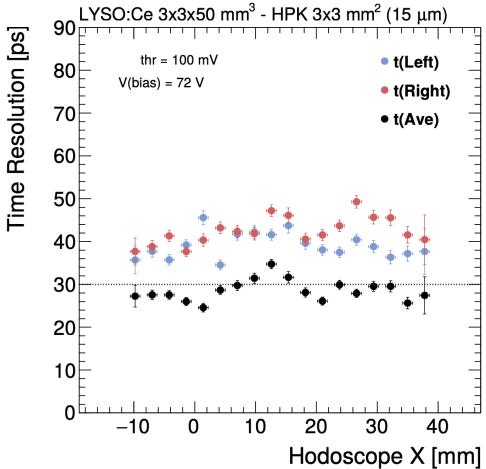

# BTL sensors: LYSO crystal and SiPM

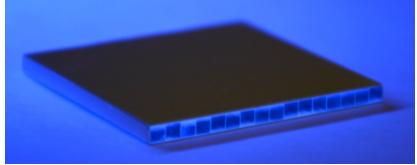

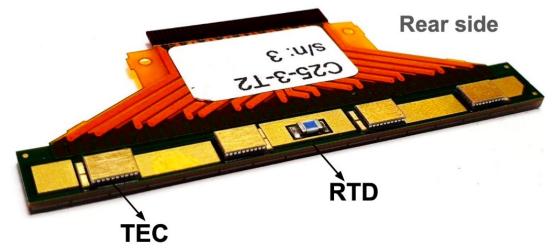

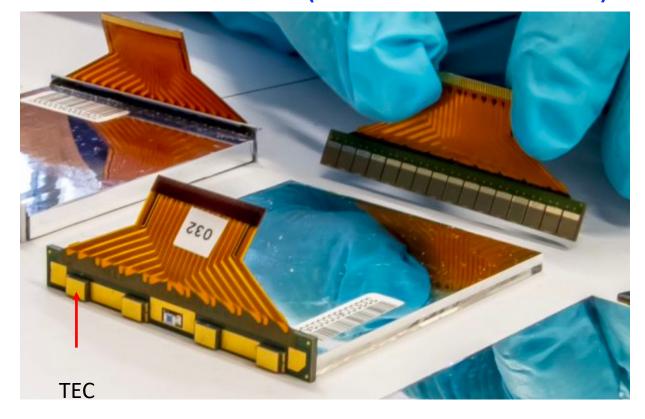

## Sensor Module (LYSO + SiPM & TEC)

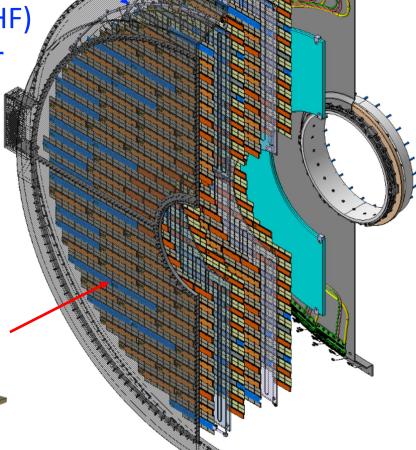

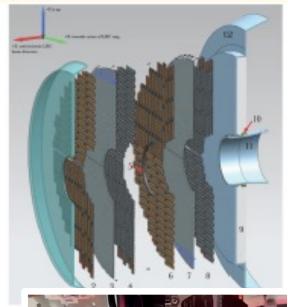

# MTD Endcap Timing Layer (ETL)

- □ Two double- sided disks for each side

- Maximize geometrical acceptance (85% per disk)

- Coverage :  $1.6 < |\eta| < 3.0$

- Average of 1.8 hits per track

- Time resolution per track < 35 ps

- based on single hit resolution < 50 ps</li>

7330 sensors

for each disk (905 kCHF)

-> 123 CHF per sensor

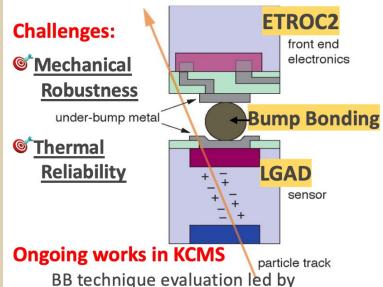

■ Low-Gain Avalanche Diode (LGAD) sensor bump bonded readout ASIC (ETROC)

Disk 2

Disk 1

31.5 cm < radius < 120 cm

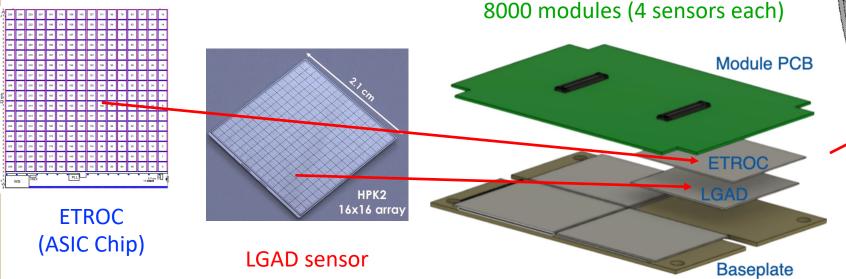

# ETL System (1) – LGAD Sensor & ETROC ASIC

# Sensor: Low Gain Avalanche Diode Phase!

Silicon-based detector with internal gain layer (Avalanche region) Achieves fast timing (30 $\sim$ 40 ps) with moderate internal gain (10 $\sim$ 30)

Key challenges: radiation hardness (~2.5×10<sup>15</sup> n<sub>eq</sub>/cm<sup>2</sup>), and maintaining Low-noise under radiation damage

High uniformity and reliability in production

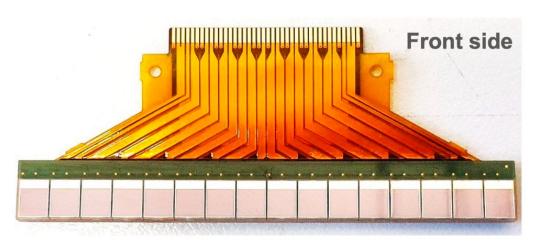

### ASIC: ETL ReadOut Chip

Readout ASIC bump-bonded directly to LGAD (TSMC 65 nm) Front-end electronics:

low noise Amplifier, fast Discriminator, and Timing Information

#### **Sensor and ASIC Procurement Status**

- LGAD Sensor: Tender (55%) launched in Apr 2025!!

KCMS in-kind contribution of 25% of total LGADs

Active production/testing ongoing: FBK, L-Foundry

(Italy), HPK(Japan) IHEP-IME(China)

USFD-K1/K2 produced at FBK (by KCMS)

- ETROC2 ASIC: Test towards PRR\* in June 2025!

\*Procurement Readiness Review

Readout Board

LGAD Sensor

➤ Module PCB

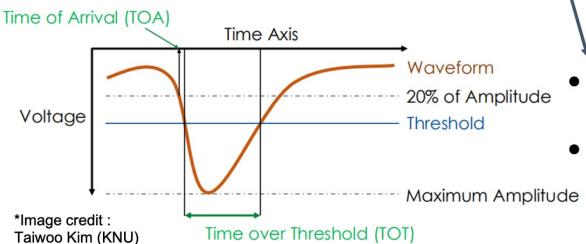

- Precise timing info extraction via **Time to Digital Converter (TDC):**Time of Arrival (TOA) and Time over Threshold (TOT)

- Key updates (2.00 → 2.02/03): Enhanced digital logic Global Readout, Calibration, Trigger, Waveform sampler

- ⇒ Less noisy and Target <40 ps time resolution per hit (system-level)

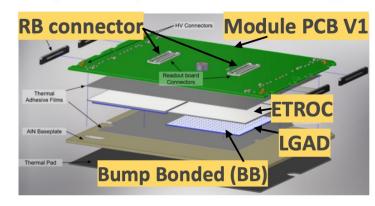

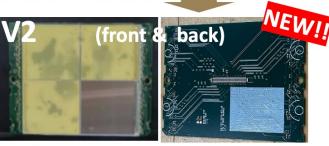

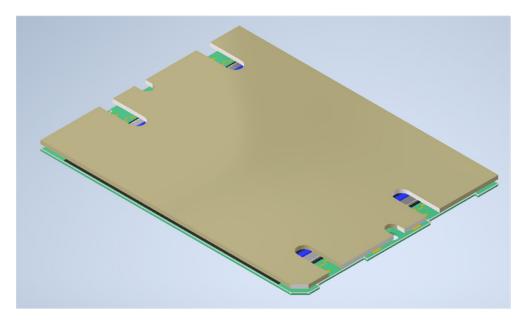

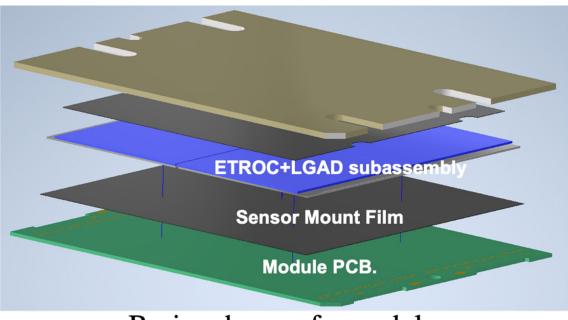

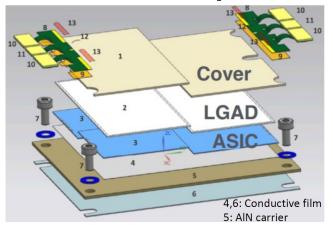

# ETL System (2) – Hybrid, Module PCB, RB

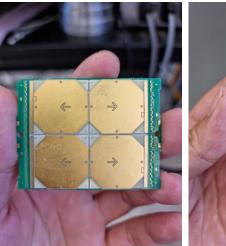

### **Hybrid (LGAD+ETROC)**

Dr. Jin Hyoung Lee (KNU)

### **Module PCB**

Early Prototype for initial test 16x16 ETROC, simple structure (∼56 ps achieved)

1st Realistic Form-Factor (RFF): Improved grounding & reduced noise(~55-80 ps)

2nd RFF: Advanced design with separate power planes (Digital/Bias/Analog), noise reduction, enhanced Bias Voltage delivery ⇒ Target ≤50 ps time resolution

### Readout Board (RB)

Connects ETROC to DAQ system (Optical fiber: VTRX+ protocol)

RB2: Stable data transmission tested in system setup with Module V0b, V1 (stable, reliable)

upgrad

e Twiki

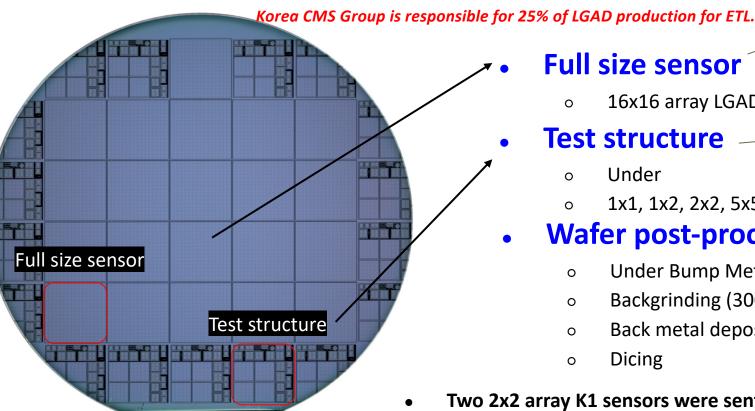

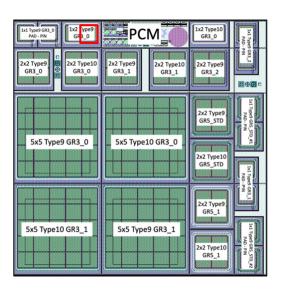

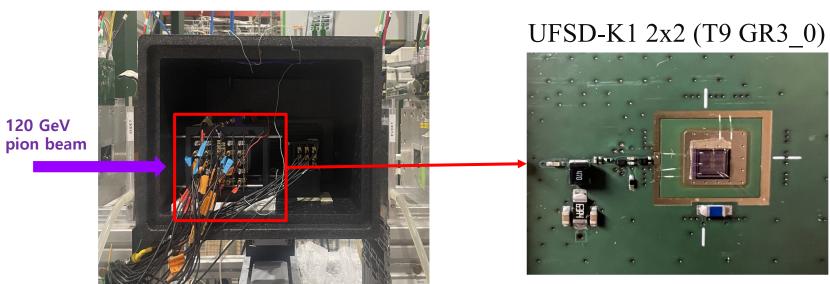

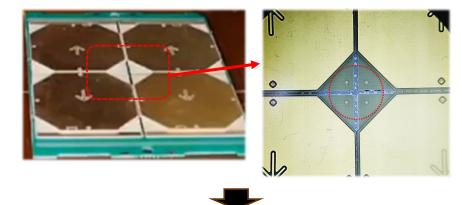

# Ultra-Fast Silicon Detector - Korea 1, 2 (UFSD-K1,K2)

### **UFSD-K1** features the prototypes of the CMS Endcap Timing Layer

- KCMS and FBK (Italy) is cooperating for production of UFSD-K1, UFSD-K2 LGAD sensors

- UFSD-K1, UFSD-K2 wafers are post-processed in Korea.

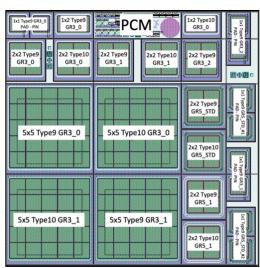

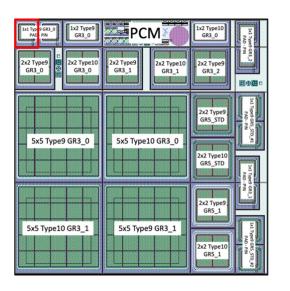

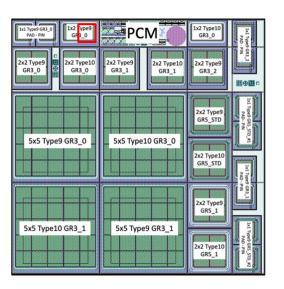

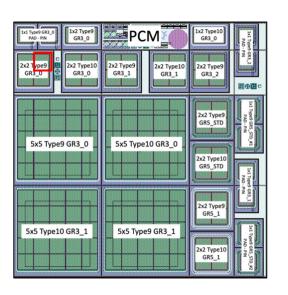

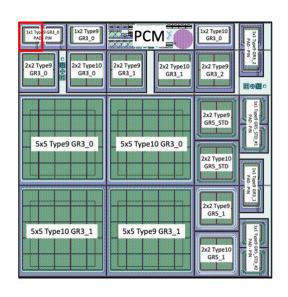

**UFSD-K1,K2 layout**

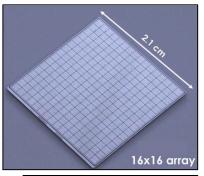

#### **Full size sensor**

16x16 array LGAD (21 x 21 mm<sup>2</sup>)

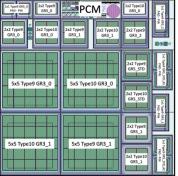

#### **Test structure**

- Under

- 1x1, 1x2, 2x2, 5x5 array LGAD sensors

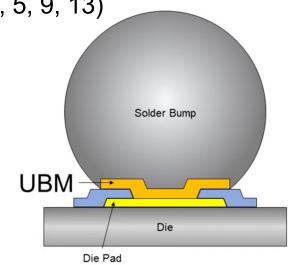

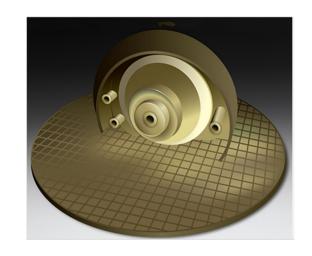

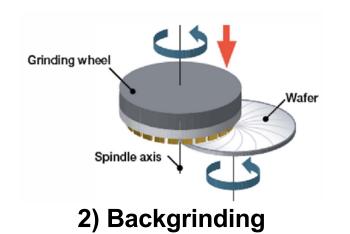

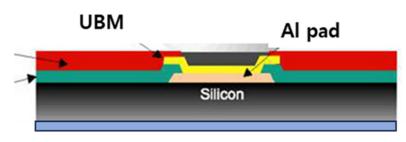

### Wafer post-processing

- Under Bump Metallization (Ni/Au)

- Backgrinding (300 μm)

- Back metal deposition (AI)

- Dicing

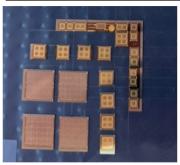

- Two 2x2 array K1 sensors were sent to Test Beam @ CERN SPS H6

- Some of the K1 sensors provided to other groups for further test.

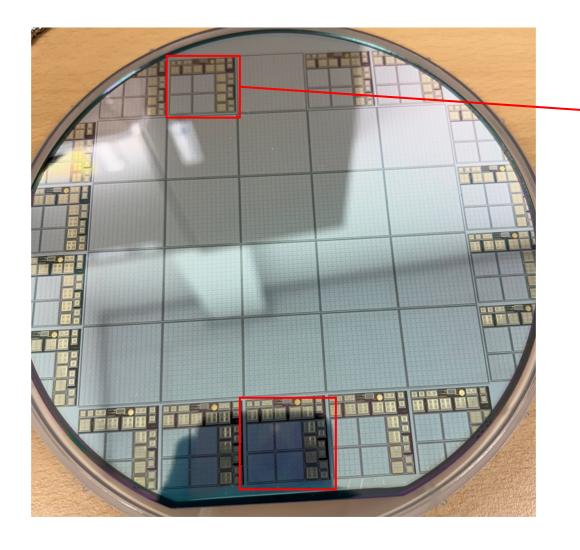

LGAD wafer

from FBK

# LGAD wafer post-processing procedure in Korea

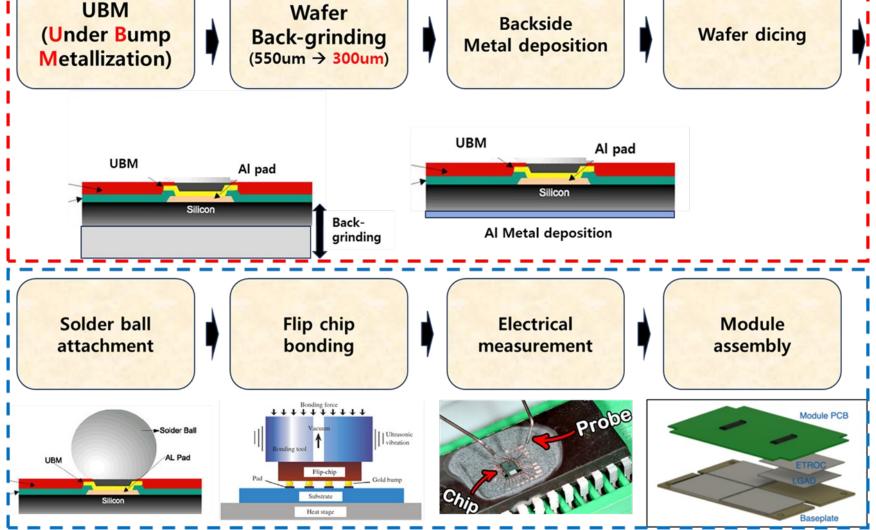

#### 1) LGAD wafer post-processing Wafer **Backside** Wafer dicing **Back-grinding** Metal deposition (550um → 300um) **UBM** Al pad Al pad Back-Al Metal deposition grinding Flip chip **Electrical** Module bonding assembly measurement

2) Bump bonding and module assembly

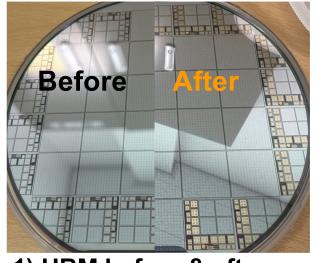

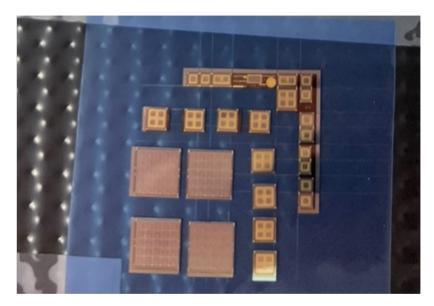

## Wafer post-processing status in Korea

- Vendors from korea completed post-processing and delivered to KNU.

- Total 5 UFSD-K1 wafers

- UFSD-K1 standard supplier wafers(# 1, 5, 9, 13)

- One new supplier wafer (# 6)

- One UFSD4 No. 14 wafer

- UBM process proceeds with electroless plating

- Thin film metal layer (Ni/Au) stack

- Backgrinding thickness = 300 μm

- Al used for backside metalization

- Dicing done with 16x16 sensor size (21mm x 21mm)

1) UBM before & after

4) Dicing

3) Al backside metalization

## Wafer post-processing status in Korea

Two test structures in each wafer were diced in detail.

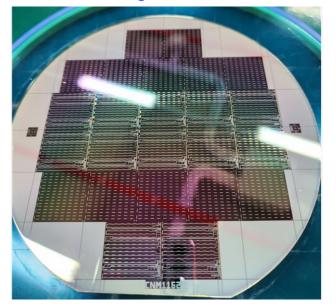

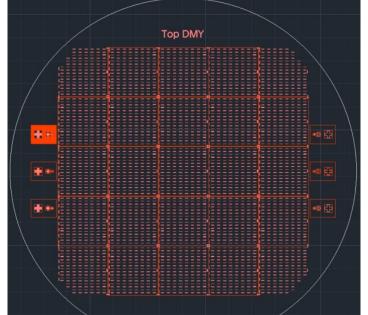

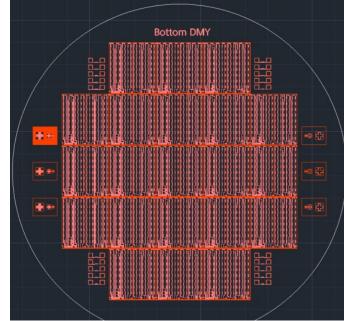

# Fabrication of dummy wafer for bump-bonding test

I designed the dummy wafers by myself and fabricated them at the ETRI fab in Korea.

- To verify the yield of the bump bonding process on a large scale.

- □ The dummy wafers have different sizes for the top and bottom parts compared to the Kansas University wafers.

- To facilitate the dicing process.

- Therefore, we made separate photomasks for the top and bottom parts.

- □ Each wafer consists of 21 main chips and test patterns on the wafer.

#### 6 inch wafer image of the Univ. of Kansas

#### 6 inch wafer design by KCMS team for dummy wafer fabrication in Korea

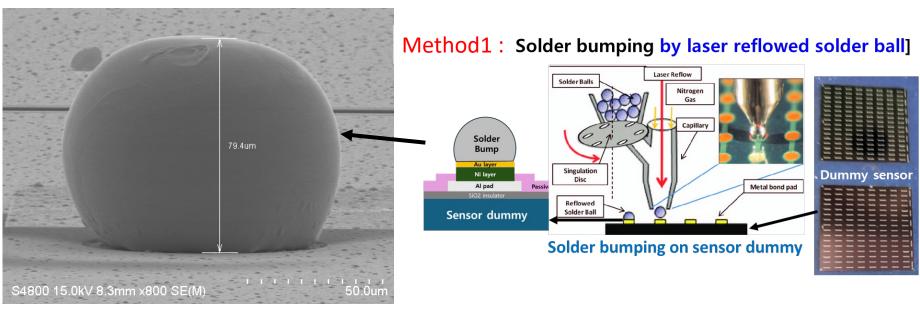

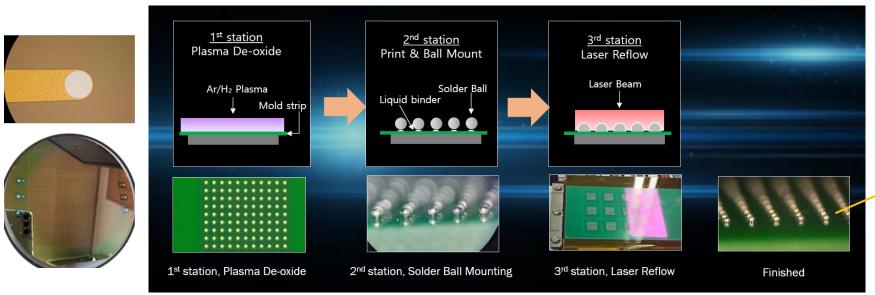

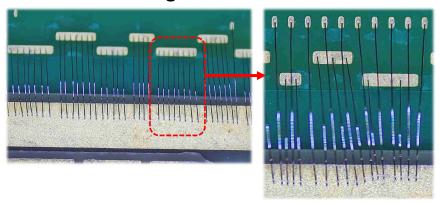

# Solder ball attachment test on dummy sensors

- Attempting three types of solder bumping process

- Laser reflowed solder ball

#### [SEM image]

- Solder bump height of ~80μm (using 100μm diameter ball)

- Good uniformity of the formed solder bump

- Out of a total of 272 pads, solder loss is minimal and, if present, is at most 1 or 2 pads

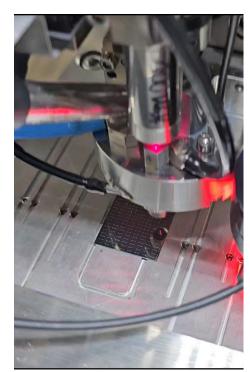

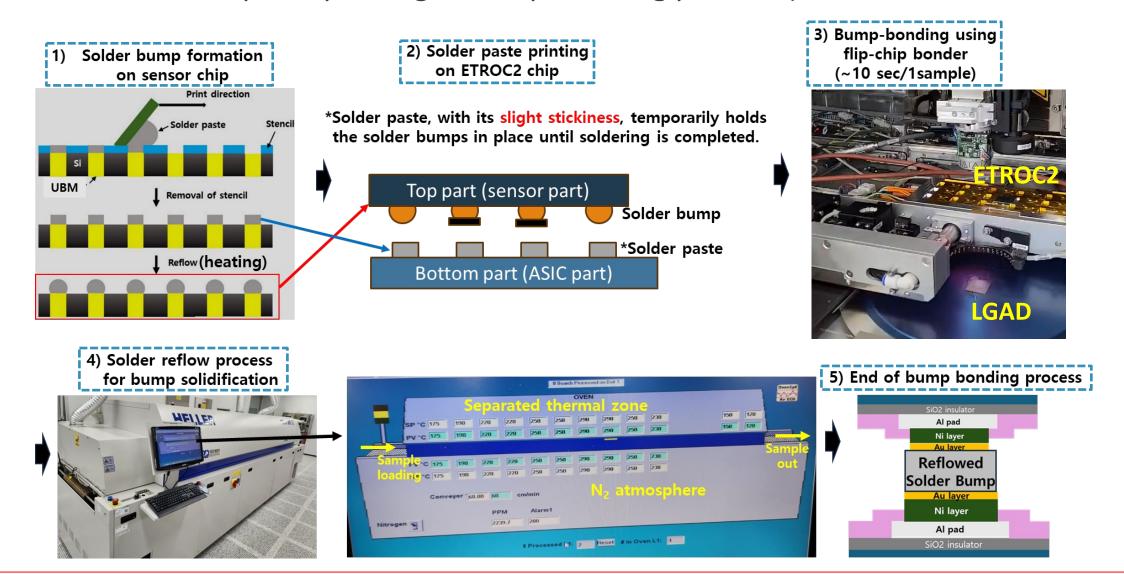

# Solder ball attachment & bump-bonding process

Method 2: Solder paste printing & Bump-bonding process (at Hansol Semiconductor)

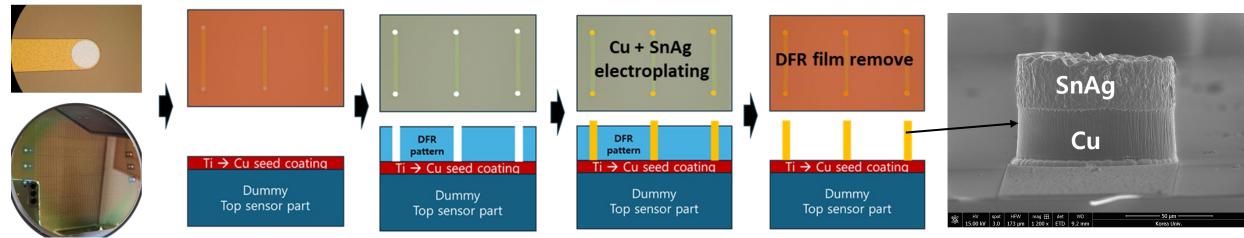

#### Method 3: [Electroplating process for solder bump formation]

Si sensor wafer

## [Solder ball attachment process for mass production of solder bump]

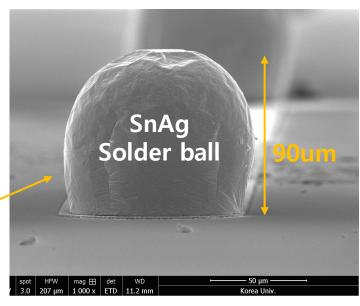

# Bump-bonding / Flip-chip bonding process

Bump/Flip-Chip Bonding is a process that creates a bump on the chip to make an electrical/mechanical connection with the chip/substrate.

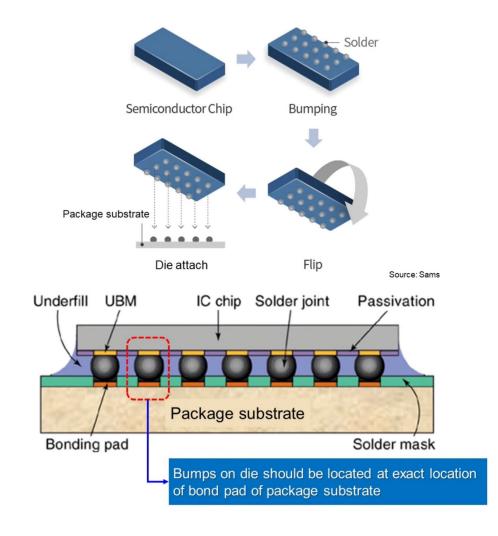

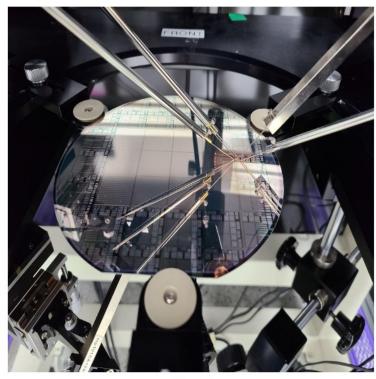

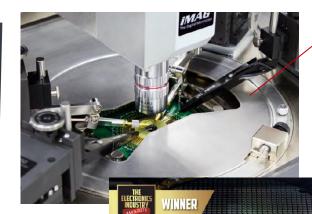

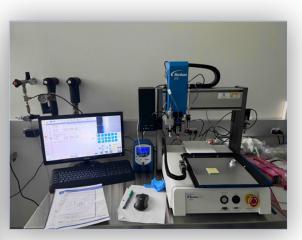

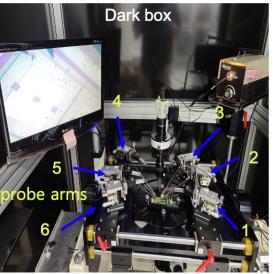

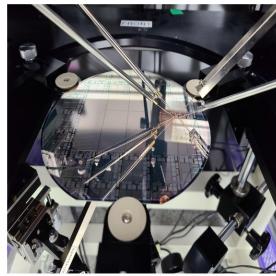

## Probe station setup for wafer-level and sensor-level tests

Overview

wafer tray

sensor tray

- ➤There are 6 probe arms that use magnets to connect with the station (1 for signal read-out, 1 for bias voltage supplying, and 4 for grounding)

- Two types of tray available for wafer-level and sensor-level tests

- ►KCMS currently has plan to prepare a **probe card** and **switching matrix for 16x16 sensors**

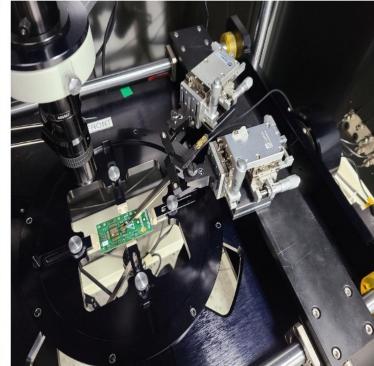

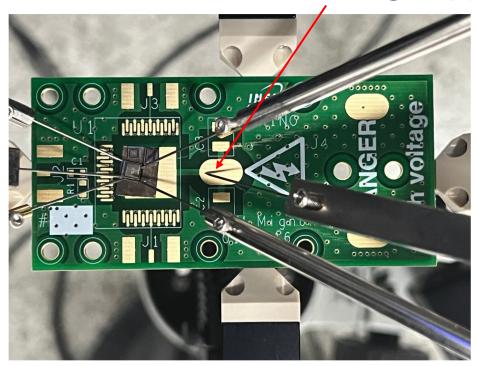

## Sensor level test at KNU

### Bias voltage apply

1x1, 1x2, 2x2 5x5 16x16

Sensors can be attached to PCB board with electrically conductive double sided tape.

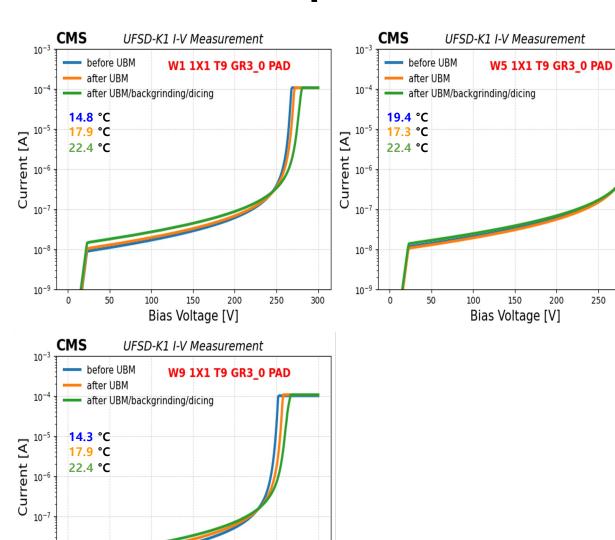

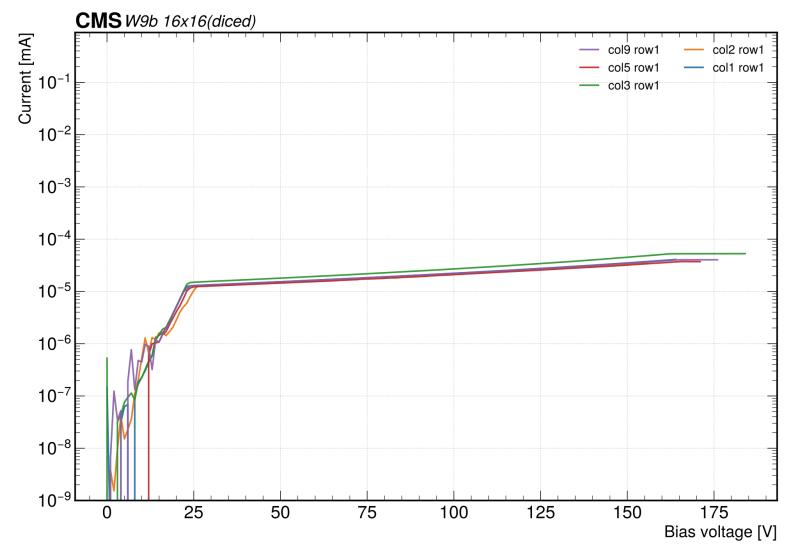

## I-V results comparison before and after UBM: 1x1 size (PAD)

300

250

Bias Voltage [V]

300

$10^{-8}$

- Current limit = 100 μA

- Bias Voltage applied up to 300 V

- Current increased after post-processing

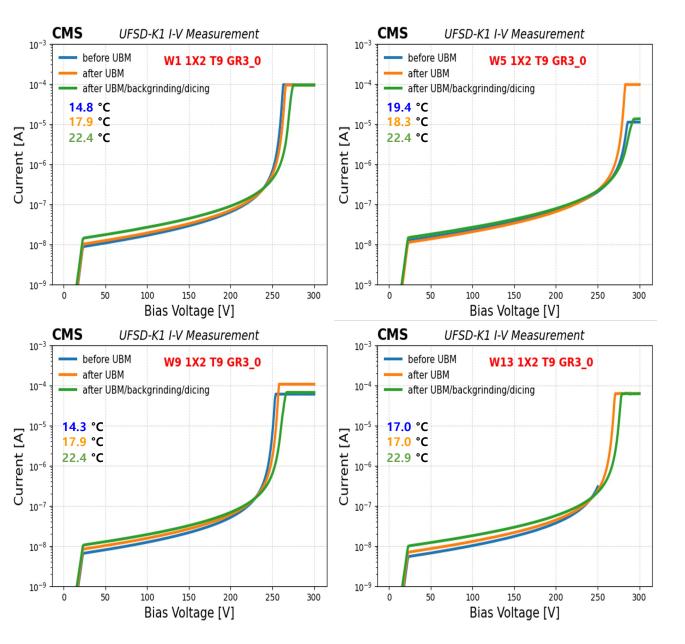

## I-V results comparison before and after UBM : 1x2 size

- Grounded other pad during measurement

- Current increased after post-processing

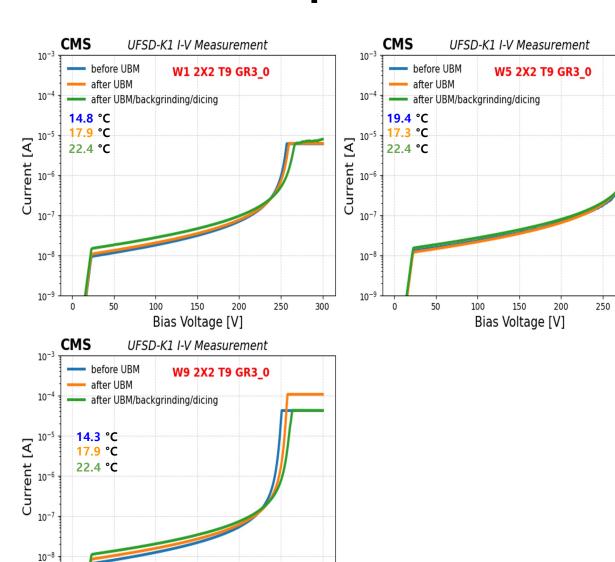

## I-V results comparison before and after UBM: 2x2 size

300

250

Bias Voltage [V]

$10^{-9}$

- Grounded other pads during measurement.

- Current increased after post-processing

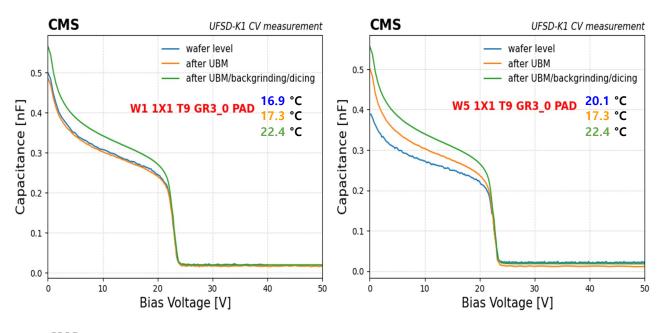

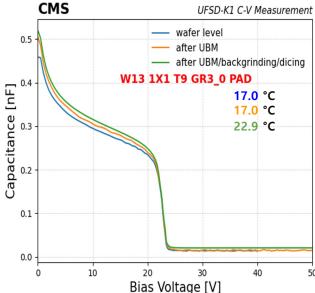

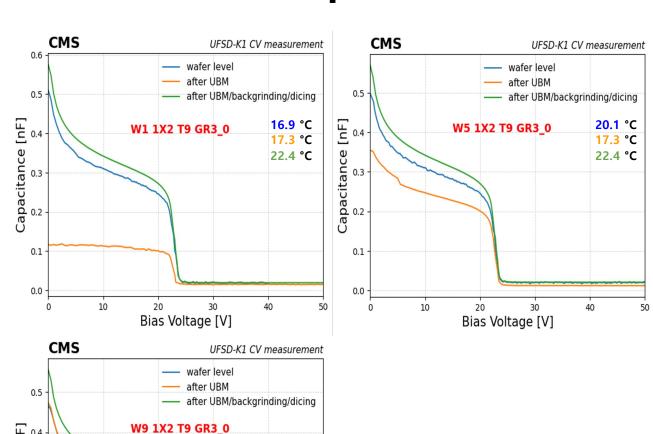

## C-V results comparison before and after UBM : 1x1 size (PAD)

- Bias voltage applied up to 60 V

- $\circ$  V<sub>fd</sub> ~ 24V

- V<sub>fd</sub> is consistent before and after the UBM.

- Difference capacitance below V<sub>fd</sub>

## C-V results comparison before and after UBM : 1x2 size

16.3 °C

18.3 °C 22.4 °C

Bias Voltage [V]

Capacitance [nF]

- Bias voltage applied up to 60 V

- $\circ$  V<sub>fd</sub> ~ 24V

- V<sub>fd</sub> is consistent before and after the UBM.

## KNU QC/QA facility setup in Korea

- 3) Automatic Probe station system setup (ready soon)

- MPI TS2000-IFE, 200mm Automated probe station

#### **Key features**

#### IceFreeEnvironment™

Enables ice-free measurements down to -40

°C using both probe cards and micro-positioners simultaneously.

Guarantees stable low-temperature operation without condensation.

#### ERS AirCool® PRIME Thermal Chuck

Temperature range : -40 °C ~ +150 °C

## Integrated Hardware Control Panel & Touchscreen

Intuitive operation for chuck control and system status monitoring.

#### Active Vibration Isolation Table

Ensures stable micro-positioning and accurate probe contact.

#### MPI SENTIO® Software Suite

Multi-touch, smartphone-like operation for prober and microscope control.

#### DarkBox Option

Light-tight enclosure for photo-sensitive device testing. Probe card mounting

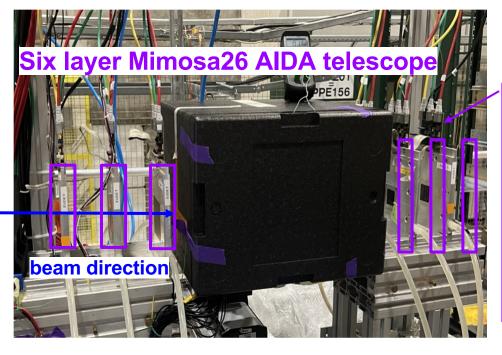

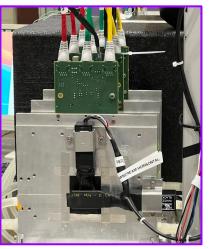

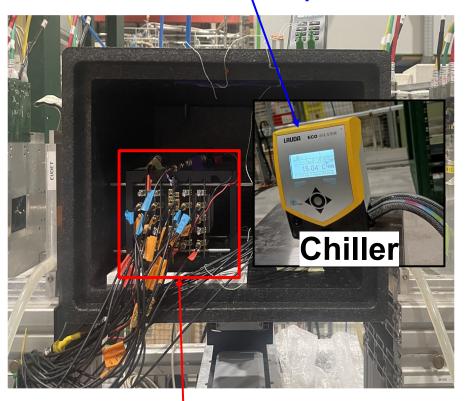

# Test Beam @ CERN SPS H6

Right side

Chiller used for constant temperature at 15 °C

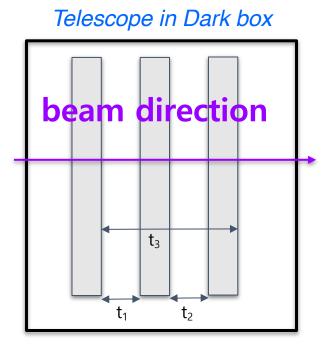

Mimosa26 telescope were used for beam quality check & tracking (left: 3 layer telescope, middle: dark box, right: 3 layer telescope)

#### 6 Santa-Cruz boards are located in the test module

- Two UFSD-K1 2x2 array LGAD sensors

- Four UFSD-LF 1x1 LGAD sensors

Datas are acquired with 8 channel oscilloscope

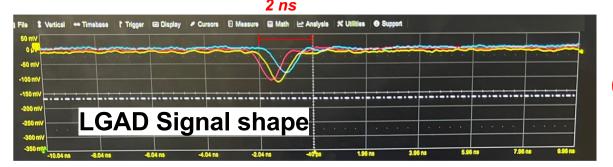

### Test Beam Results for LGAD sensors at CERN

Test beam were carried out by KNU and Torino group at SPS H6

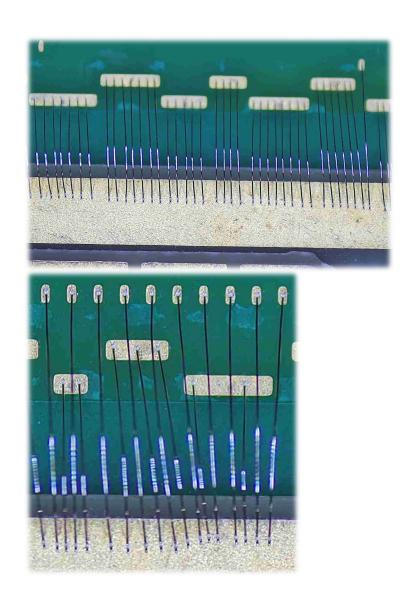

PCB wire bonding layout

Time resolution of each sensors are extracted by following formula

$$\sigma^{2}_{i} = (\sigma^{2}_{i,j} + \sigma^{2}_{i,k} - \sigma^{2}_{j,k})/2$$

$\sigma_{1} = 32.34 \text{ ps}$

$i \neq j \neq k$   $\sigma_{2} = 35.04 \text{ ps}$

$i, j, k \in [1,2,3]$   $\sigma_{3} = 33.30 \text{ ps}$

Dark box chilled to 15 °C

LGADs has been reached 35 ps timing resolution.

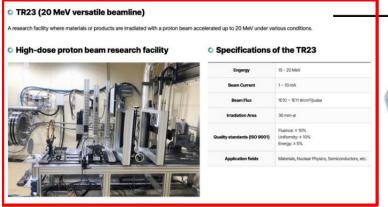

## Irradiated LGAD sensors at KOMAC in Korea

### **KOMAC** (Korea Multi-purpose Accelerator Complex)

For both room, beam flux would be 1E10-1E11/pulse

- → Depend on the beam status

- → Beam size: 30 mm ø

- insure the fluence within 10% uncertainty

- Outside the area beam is still active

- → only use single sample per each irradiation

- With 100 MeV beam, deposited dose is so small and expect larger irradiation time

- → Decide to use 20 MeV beamline (TR23)

**North Korea**

\*h Korea

Gyeongiu

Pyongyang 평양

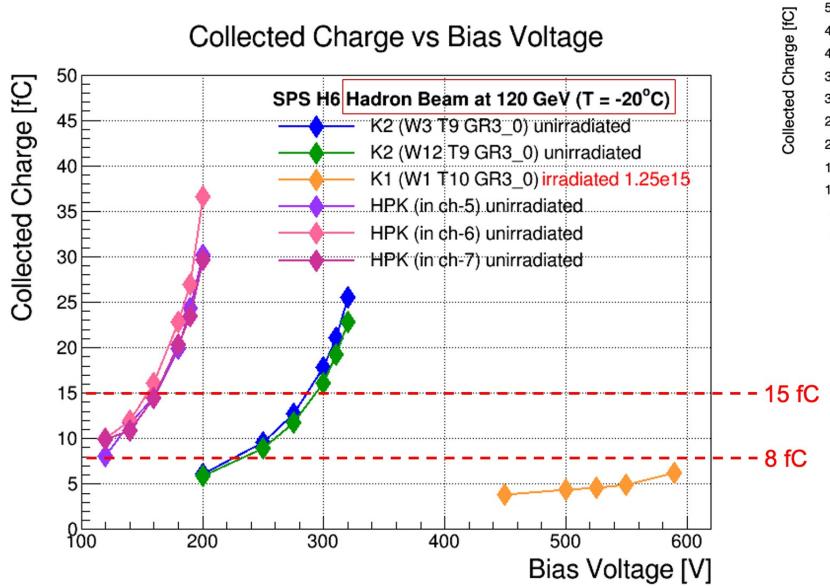

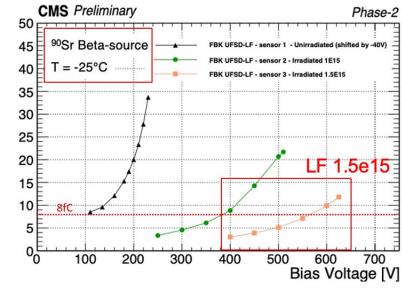

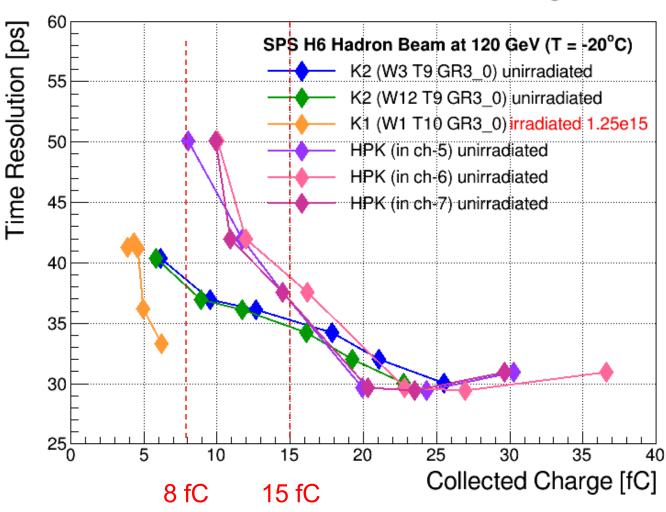

## Collected Charge vs Bias Voltage using CERN test beam

Characterization of the FBK-LGAD devices manufactured at an external foundry for large-volume productions, Leonardo Lanteri

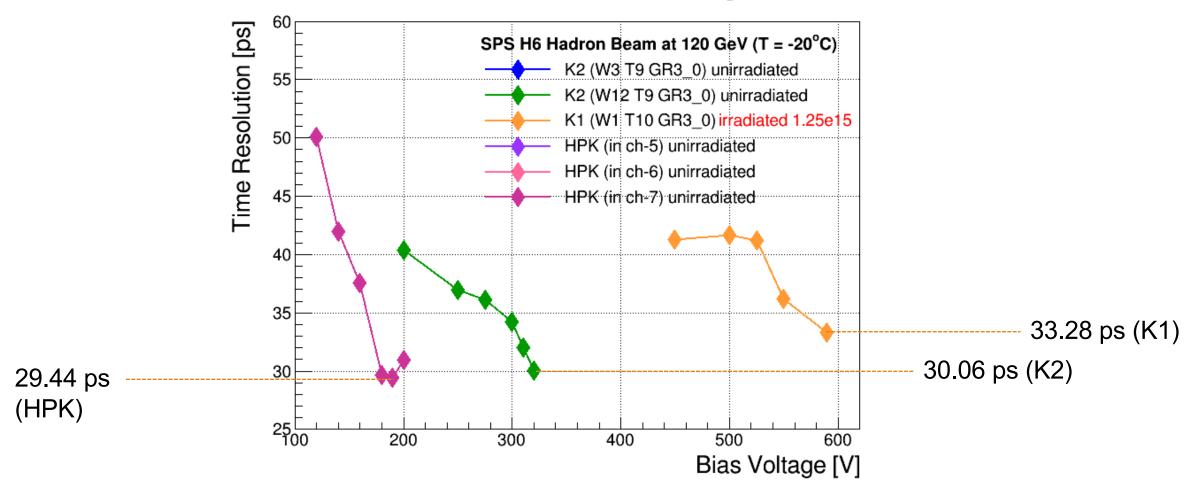

## Timing Resolution vs Bias Voltage using CERN test beam

#### Time Resolution vs Bias Voltage

## Timing Resolution vs Collected Charge using CERN test beam

### Time Resolution vs Collected Charge

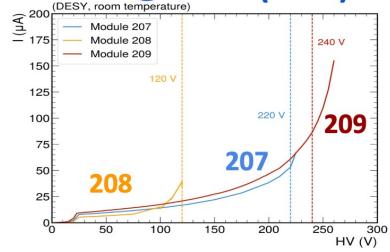

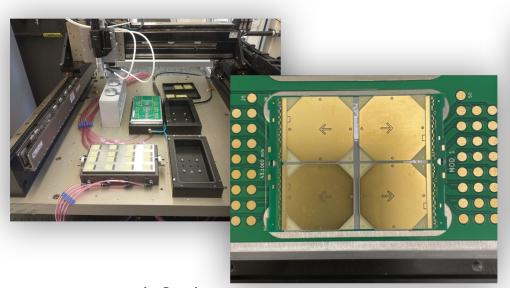

# Test Beam @ DESY for bump-bonding quality test

### IV Scan @ DESY (15°C)

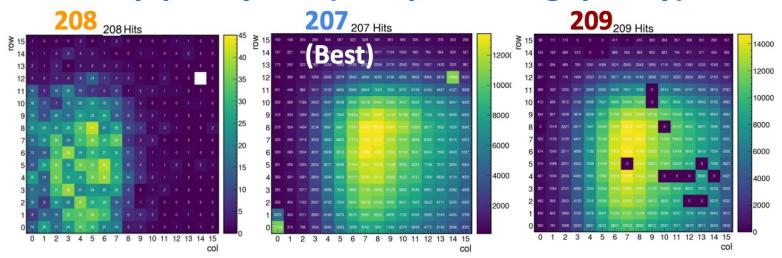

## Hit map per hybrid (Bump-bonding quality)

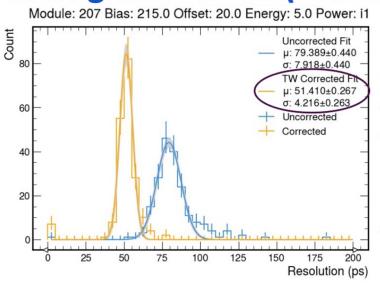

## **Timing Resolution (Module 207)**

### Highlights

- Collected >30 M events over 1 week (Single 207, 209 + Dual 207–208 modules)

- Stable DAQ up to 1.5kHz trigger rate  $\Rightarrow$  Highest stat. ever in ETL system test!

- Good performance:

- Solid Bump-bonding quality in 207, 209 (MICROSS)

- Achieved 51-56 ps time resolution (after time walk correction) with 207, 209

- More interesting results will be updated!

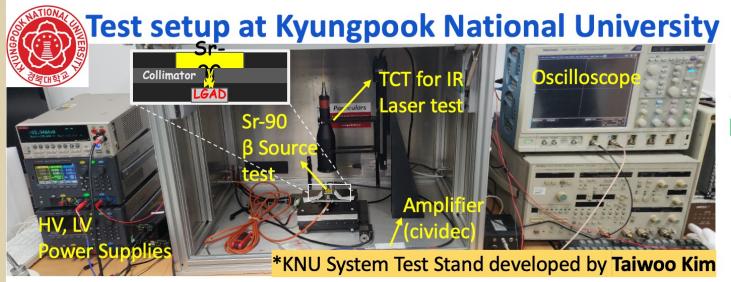

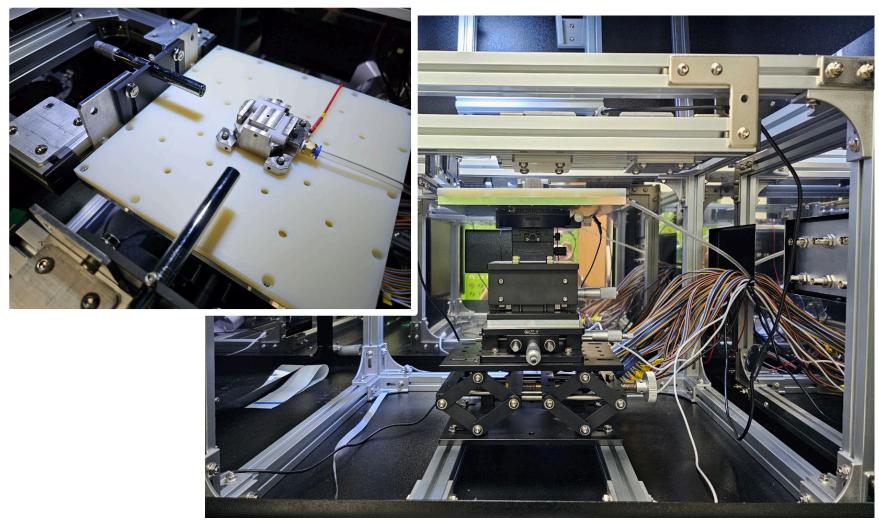

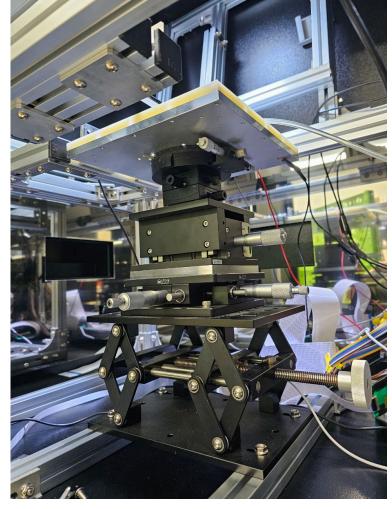

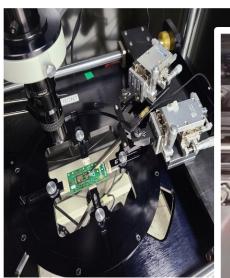

# Test Stand for ETL System Test at KNU

### **Status and Updates**

- **Update Laser** setup to **β source** setup with Sr-90

- **▼ Performance test for UFSD K1-LGAD** before IRRAD Test @KOMAC

IV Scan & Charge Collection (Pre-Irradiation baseline)

Done in 5x5 array using Laser and Sr-90 source with only-scope data (No ETROC data due to RB-FPGA lpGBT connection issue)

- ☑ Recently, the issue was resolved by updating "Clock config"

in FPGA (Debugging & Verified at CERN Test Setup in B.904)\*

- ETROC data integration (with hybrid module): To be updated

### **Test Source Versatility @ KNU**

### IR Laser setup β Source setup

Precise time calibration and ic charge collection measurement

Next plan

Mimic minimum full-size hybrid ionizing particle (MIP) module testing, response from Sr-90 cosmic setup cooling test, etc ...

# Test setup at CERN (Bld.904) Apr.9th 20 FPGA Readout Board (RB2) Optical Fiber Cable VTRX+ RB2-FPGA connection debug completed

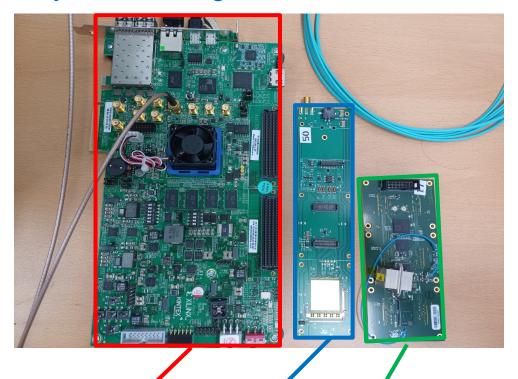

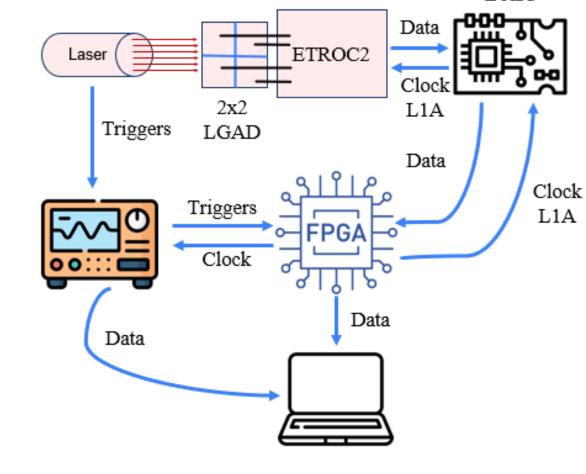

### MTD – Endcap Timing Layer (ETL) System Test at KNU

Readout Board

System Test Ingredient @ Korea

**FPGA**

Module v0b

Readout Board v2.2

- System test stand for LGAD + ETROC system

- System test setup are constructed in Korea.

- Using this test stand, we can measure entire timing performance.

- We are planning to test with ETL Module v1 and v2 as well.

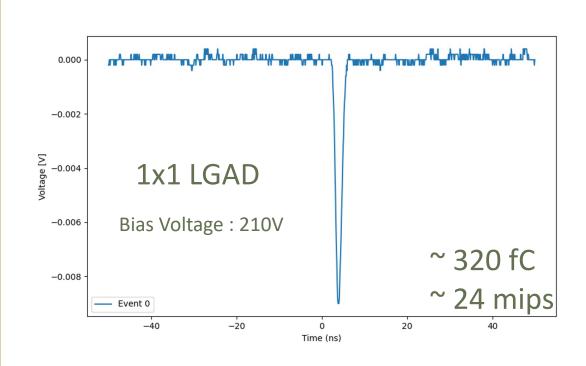

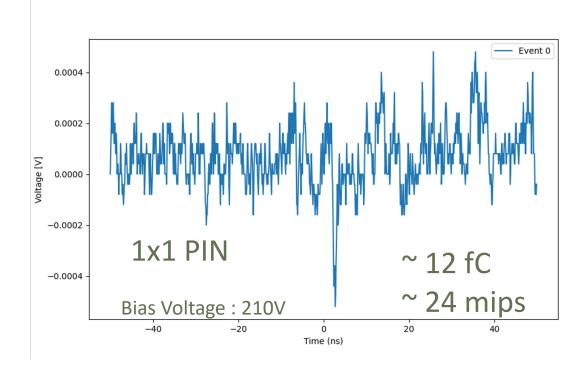

# Pulse shape from LGAD using laser (V<sub>Bias</sub> = 210)

### V<sub>Bias</sub> measurement range:

- LGAD : 140 ~ 210 V

- PIN Diode: 160 ~ 210 V

Gain ~ a factor of 27 (1 mips ~ 0.5 fC)

• Laser Width: 81%

DAC value : 2673 mV

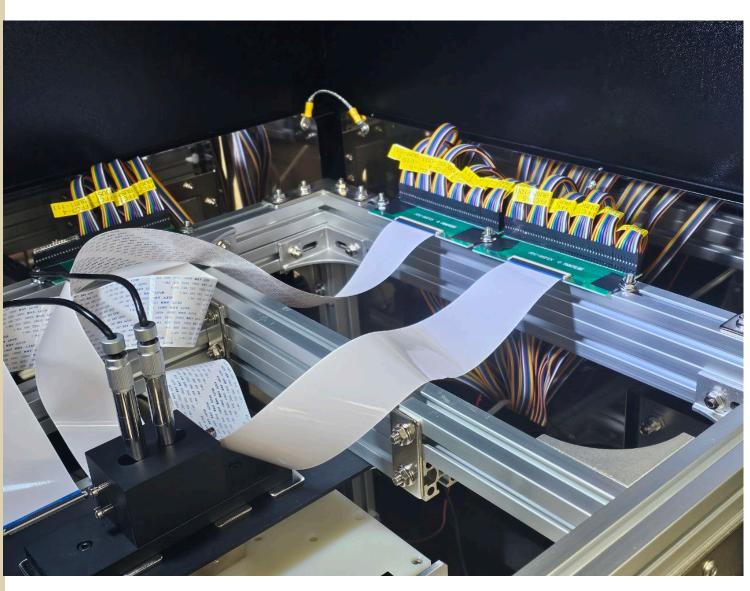

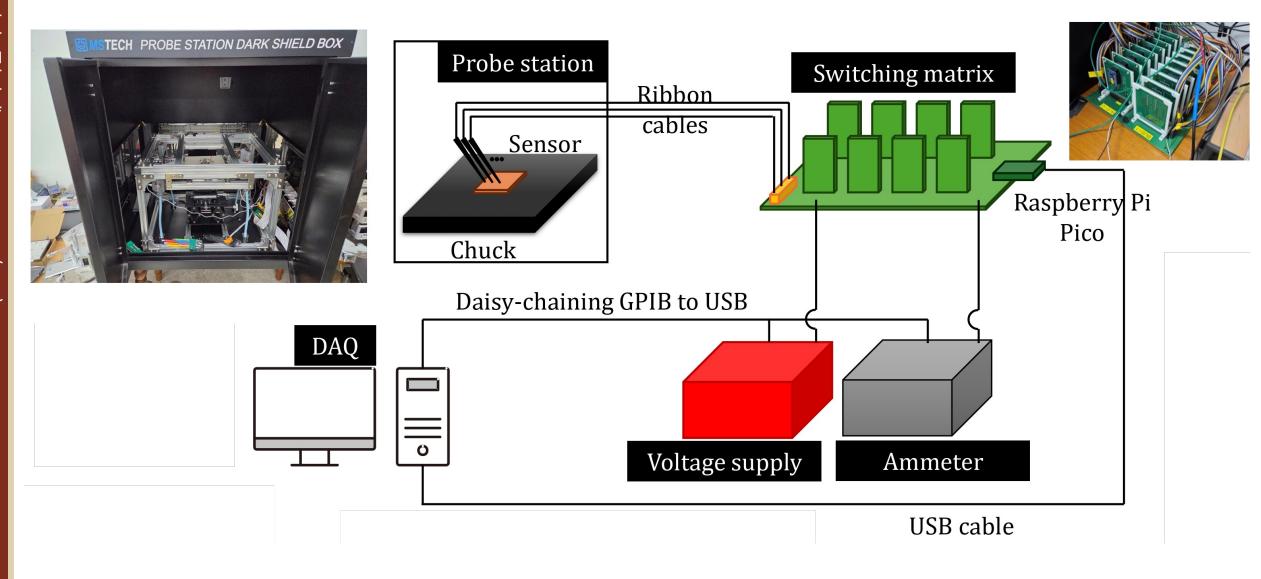

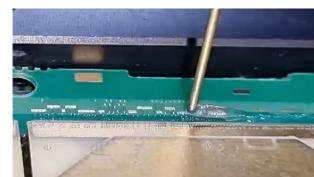

### Development of probe card jig system test bench for LGAD QA/QC test

- Development of a probe card jig system integrated with a switching matrix

- Manual probe card jig system to prepare a QA/QC tes using an automated probe station

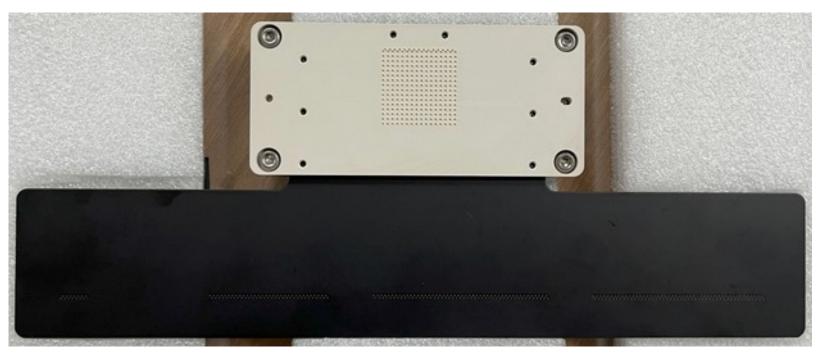

### Probe card design

# Front

# Back

Readout cable connectors

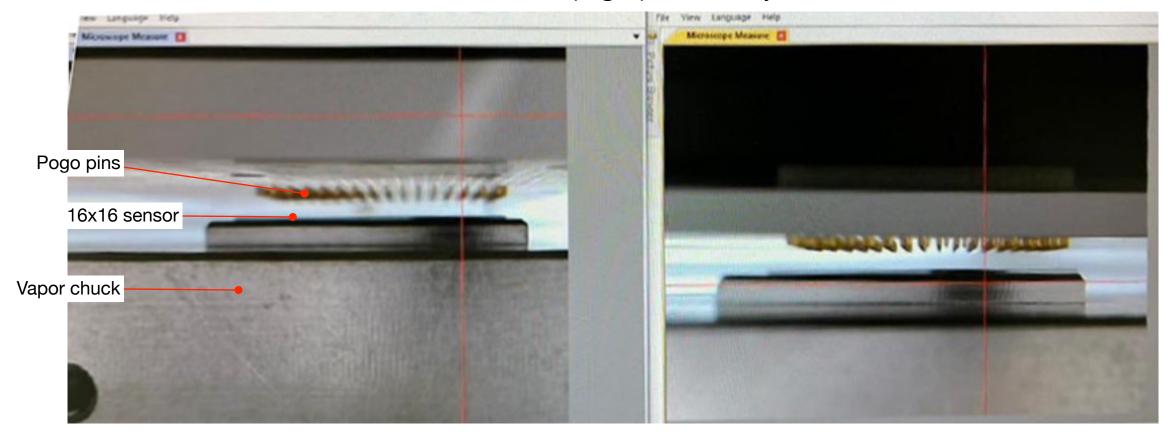

# **Probe Card 256 channel Switching Matrix System**

# Pogo pins contact

Contact between sensor and pogo pins seen by two side usb cameras

- Using two USB cameras, we adjust the tilt and the distance between the sensor and the probe card using the tilt and z stages.

- Checking good contact

- > Using a multimeter to confirm the connectivity between the two outermost BBs though the probe card.

- > If they are connected we assume the contact is good.

# Probe card jig system DAQ workflow

### IV measurement results with the current jig system

- Measured 5 different pads by manually changing the channels

- The IV curves look reasonable and are consistent each other

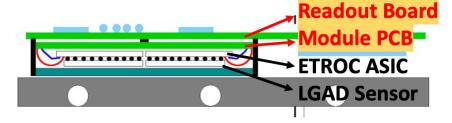

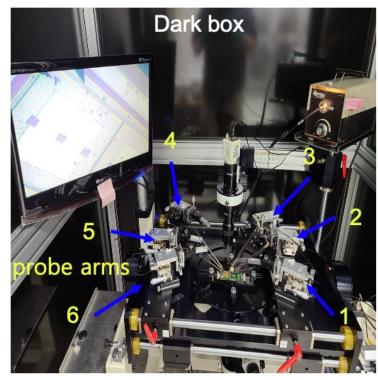

# ETL Module design overview

### ■ Module design overview

PCB + subassembly

Basic scheme of a module

- □ Module PCB

- Printed circuit board that serves as the power and readout interface for the module

- □ 4x ETROC+LGAD subassembly

- 2x2 arrangement of bump-bonded assemblies

- Each of a 16x16 pixel LGAD sensor and an "ETROC" readout chip

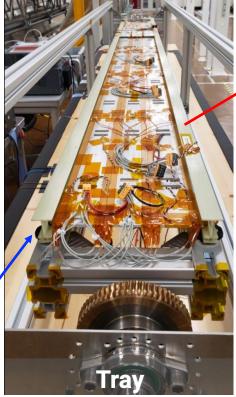

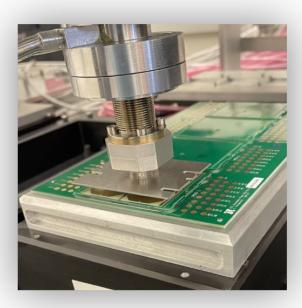

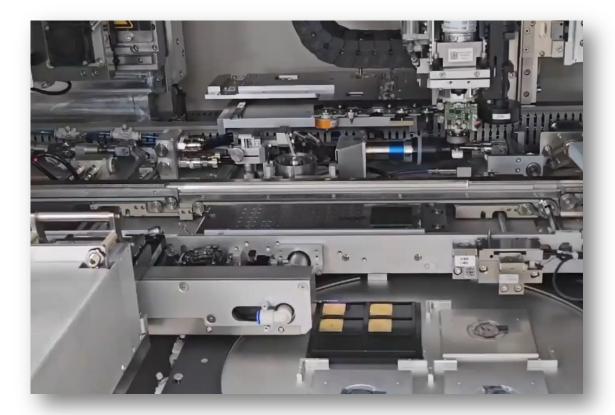

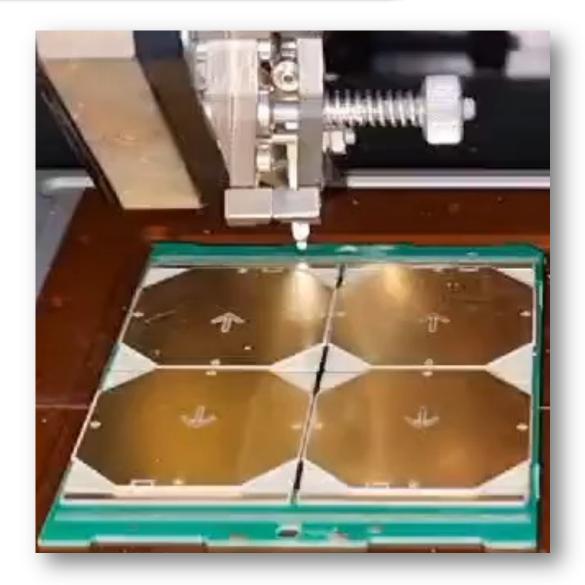

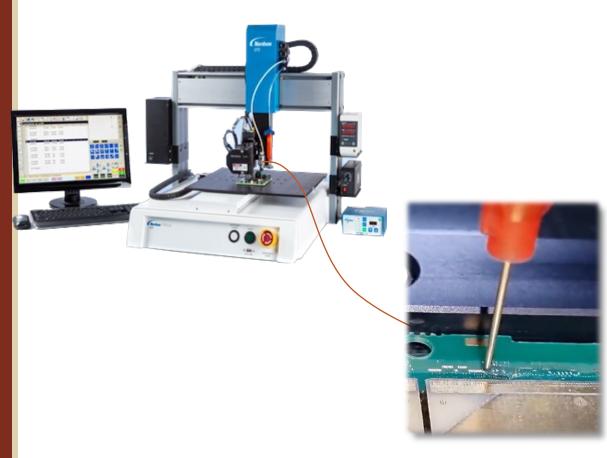

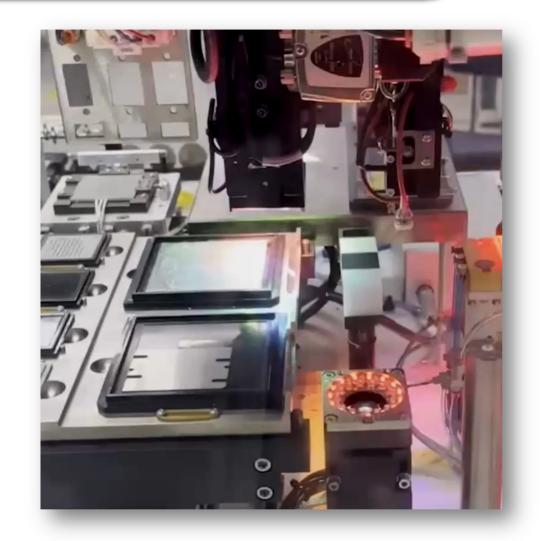

# **Assembling the ETL Modules**

- □ The ETL detector will need ~8 thousand modules

- □ Each module will be made of 4 LGAD sensors and ETROCs

- □ An automated robotic gantry will be used for precision placement at the 10 micron level

- □ All modules will then be assembled into disks at CERN

Pick & place sensor + PCB

Wirebond and encapsulating

Apply film to baseplate, pick and place, and cure film

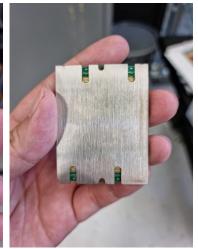

# Module assembly test with dummy sample

- Module assembly pre-test for final product

[Module assembly concept of LGAD sensor]

#1. Die attach of Bump bonded sample

#2. Wire bonding to PCB board

#4. Base plate covering

#3. Wire passivation with glue

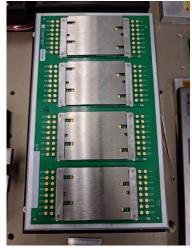

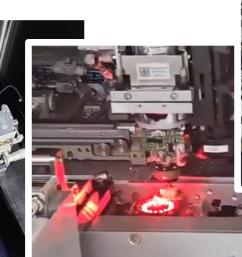

# **ETL** Module Bonding

### comparison

TOTAL WORKING TIME = 16sec / 1Chip

**TOTAL WORKING TIME = 1min / 1Chip**

**Korean vendor – die bonder machine**

Fermilab – Gantry system

# ETL Module Wire Bonding

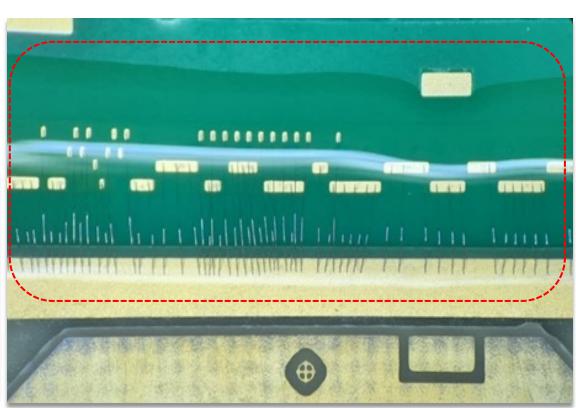

# ETL Module Encapsulation

**MEMSPACK**

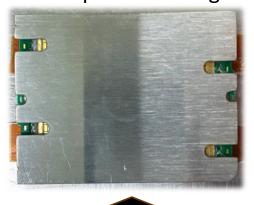

# ✓ ETL Module Base Plate Bonding

반도체 PACKAGING 장비

### • CERN Gantry system issue

- Inaccurate position of baseplate

- Unable to place automatically for current component condition

- Bumpy surface of baseplate makes lift

- Vacuum leakage issue

## KCMS contribution for MIP Timing Detector (MTD)

Mitigate the pileup effects at HL-LHC using precision timing information to enhance and expand the physics reach our detector performance.

### Main contributions from KCMS

- Low Gain Avalanche Detector (LGAD) sensor development & production

- LGAD & ETROC Bump-Bonding development & processing

- ETL (Endcap Timing Layer) Module Assembly development & production

KCMS contribution for MTD : 2.2 MCHF (25% of the total endcap coverage)

Total contribution with MTD on the Phase 2 will be ~6 MCHF

Overview

wafer tray

# **Current Korea CMS Activities and Future plan**

- □ Significant contributions to prototyping towards production

- □ LGADs prototyping and validation

- Detailed testing of prototype LGADs informed vendor qualification

- Probe station measurements to verify quality and uniformity of full-size wafers

- Preparing the test bench setup with probe card and switching matrix

- Participating various test beam at CERN and Fermilab

- System testing with LGAD+ETROC

- Will receive 12-inch ETROC2 wafers from CERN

- Active in System testing with LGAD+ETROC2, including test beam campaigns for validation of the performance of the LGADs +ETROC chain

- LGAD Wafer processing

- Exploring wafer processing with one of the qualified LGADs vendors for wafer thinning, dicing, and surface preparation at Korean companies for the production phase

- Bump-bonding processing

- Process testing with Korean vendors for LGAD-to-ETROC bump-bonding during production

- Module assembly

- Korean vendor (Memspack) showed excellent performance for module assembly process with the die bonding machine.

- Plan to irradiation test for encapsulation and glue using the KOMAC test beam October and December.